数字集成电路设计中的硬件加速验证技术

随着半导体工艺的不断进步,数字集成电路的规模和复杂度呈指数级增长,这给传统的软件仿真验证方法带来了前所未有的挑战。在芯片设计流程中,功能验证是确保设计正确性的核心环节,其耗时往往占据整个设计周期的70%以上。为了应对验证瓶颈,硬件加速验证技术应运而生,并已成为现代集成电路设计,尤其是大规模SoC(片上系统)设计中不可或缺的关键技术。

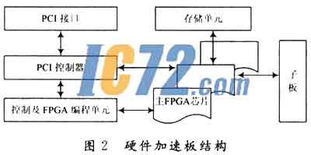

硬件加速验证的核心思想,是利用专用的硬件平台来执行验证任务,从而获得比纯软件仿真高出数个数量级的运行速度。这项技术主要包含两大分支:基于FPGA的原型验证和专用硬件仿真器。

一、基于FPGA的原型验证

这是目前应用最广泛的硬件加速形式之一。设计团队将待验证的RTL(寄存器传输级)代码综合并映射到一个或多个高性能FPGA上,构建出一个能够以接近真实芯片工作频率运行的物理系统。FPGA原型验证平台的优势在于其极高的运行速度,通常可以达到几兆赫兹到几十兆赫兹,这使得工程师能够运行大规模的软件测试向量、启动嵌入式操作系统,并进行软硬件协同验证。这为早期软件开发、系统性能评估和架构探索提供了无与伦比的便利。FPGA原型验证也面临一些挑战,例如将复杂的ASIC设计移植到FPGA架构时可能遇到时序、内存模型和时钟域处理等问题,需要一定的设计适配工作。

二、专用硬件仿真器

专用硬件仿真器(Emulator)是另一类强大的硬件加速验证工具。它采用大规模可编程处理器阵列或定制化处理器,通过编译将设计映射到其硬件结构上运行。与FPGA原型相比,仿真器的优势在于其出色的调试能力和可控性。它通常提供全可视化的调试环境,支持对设计中任何信号在任意时刻的状态进行监测和设置断点,其运行速度虽不及FPGA原型(通常在几百千赫兹到几兆赫兹量级),但远快于软件仿真。现代仿真器通常支持事务级建模和加速,允许验证环境在主机服务器上运行,仅将DUT(待测设计)部分下载到仿真器中,通过高速链路进行通信,极大提高了验证效率。

三、硬件加速验证的技术价值与挑战

硬件加速验证技术的价值不仅体现在速度的提升上,更在于它改变了验证的范式。它使得在流片前运行完整的系统级场景测试、进行功耗和性能的实时分析成为可能,显著降低了流片风险,缩短了产品上市时间。

该技术也伴随着挑战。首先是成本问题,无论是构建FPGA原型平台还是购置专用仿真器,都需要巨大的前期资本投入。其次是使用的复杂度,搭建和维护硬件验证环境需要具备硬件和软件的跨领域专业知识。最后是容量限制,尽管硬件平台的容量在不断增长,但对于超大规模的芯片设计,仍可能需要进行设计分割或采用多板卡互联方案,这增加了验证的复杂性。

四、未来发展趋势

硬件加速验证技术正朝着更高集成度、更智能化、更云化的方向发展。云计算资源的引入使得硬件仿真能力可以作为服务提供,降低了中小设计公司的使用门槛。与人工智能和机器学习技术的结合,使得验证过程能够自动分析覆盖漏洞、智能生成激励,实现验证的自动化和智能化。随着Chiplet(芯粒)和异构集成技术的兴起,硬件验证平台也需要适应这种模块化、多裸晶粒的设计验证需求。

硬件加速验证技术是数字集成电路设计迈向更高复杂度与更高可靠性的关键引擎。它弥合了软件仿真与真实芯片之间的鸿沟,是确保一次流片成功、赢得市场竞争的重要保障。随着技术的不断演进,它必将在未来的芯片创新中扮演更加核心的角色。

如若转载,请注明出处:http://www.gdyuezhi.com/product/7.html

更新时间:2026-04-26 20:55:52